Luisier wins SNSF Advanced Grant to develop simulation tools for nanoscale devices

By Carey Sargent, EPFL, NCCR MARVEL

The Swiss National Science Foundation has awarded Professor Mathieu Luisier more than two million Swiss francs over a period of five years to develop a computer-based simulator that will simplify the design of electronic components and speed up their fabrication process.

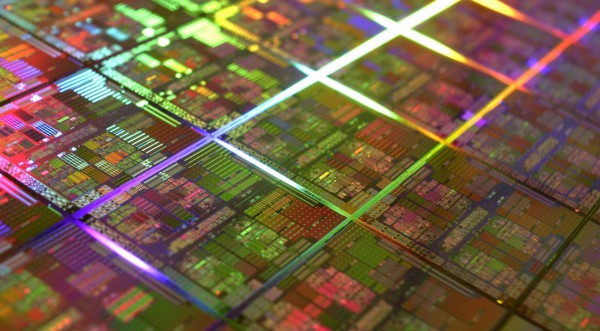

Moore’s scaling law, which observes that transistor sizes decrease at an exponential rate, has seen the dimensions of these components, which form the heart of semiconductor chips, approach the atomic limit. Quantum mechanical effects dominate here and developing and producing reliable devices at this scale is complicated—Intel, for instance, had to delay introduction of its 7-nanometer chip by four years while it went back to the drawing board on transistor design.

While complicated, it’s also the way ahead: smaller transistors mean that more can be fit onto a piece of silicon, making it possible to build more powerful and complex components. Luisier envisions, for example, the co-integration of light emission/detection modules that enable high-speed intra-chip communication, thermoelectric generators that help recycle the heat dissipated by microprocessors and non-volatile memories that will allow for energy-efficient data storage.

These innovations and new functionalities will only be possible though if novel materials such as, for example, two-dimensional materials, inorganic compounds such as BaTiO3 and complex oxides can be combined with the silicon that forms the basis of these chips. In addition to the integration of novel materials, all of these functionalities involve electrical, optical, and thermal effects. They lead to important interactions between electrons, phonons, and photons that could, in turn, have a negative impact on the performance of electronic devices and so should be engineered and controlled already during the initial design phase.

Moore’s law has held until now, Luisier says, because of the continuous adaptation of transistor fabrication recipes and the gradual introduction of technology boosters such as strain or 3D FinFETs. This progress, while driven by the intuition of visionary researchers, has been underpinned by classical technology computer aided design (TCAD) tools that served to validate new ideas.

Device engineers have however realized that such design approaches cannot handle the atomic scale because of the strong influence of quantum mechanical effects. Combining multiple functionalities, mixing heterogeneous materials and the close interaction between electrical, thermal and optical phenomena complicate the situation further. The design of next-generation chips, Luisier says, will depend on the availability of advanced modelling tools that can be used during the design process to accurately predict the characteristics of multi-functional, multi-material nano-devices.

While more advanced modelling tools exist—including one, OMEN, developed by Luisier himself—their practical use is limited by various considerations. In some cases, they can only be used in tiny structures of fewer than 1,000 atoms, use empirical parameters as inputs, or ignore certain particle-particle interactions, for instance. Researchers need a new class of device simulators with enhanced modelling capabilities.

This is where the SNSF-funded Quantum Transport Simulations at the Exascale and Beyond project comes in—its ultimate goal is to go “beyond state-of-the-art” with the development and release of an open source, general-purpose, portable, scalable, and advanced device simulator, “QuaTrEx”. The tool will feature unique abilities and set new standards in terms of simulation capabilities, code implementation and device applications.

“By accounting for the proper physics, by offering a large palette of device geometries, by leveraging all types of computing resources, and by being released as an open-source software, the proposed QuaTrEx tool has the potential to accompany the semiconductor industry during at least 20 years, save it from design issues that might result from inaccurate predictions provided by standard device simulators, and pave the way for next-generation semiconductor chips,” Luisier said.

The SNSF funding will support two post-docs and three PhD students throughout the project duration.

The SNSF Advanced Grants were introduced in 2021 to provide researchers at Swiss institutions a substitute for European Research Council Advanced Grants, for which they are currently ineligible to apply: Switzerland is considered a non-associated third country by the EU’s Horizon Europe research program. Of 232 Advanced Grant applications submitted to the SNSF last year, 24 qualified for funding.

Low-volume newsletters, targeted to the scientific and industrial communities.

Subscribe to our newsletter